- 您现在的位置:买卖IC网 > Sheet目录3882 > PIC16F77T-I/ML (Microchip Technology)IC MCU FLASH 8KX14 A/D 44QFN

Micrel, Inc.

KSZ8851-16MLLJ

March 2010

49

M9999-030210-1.0

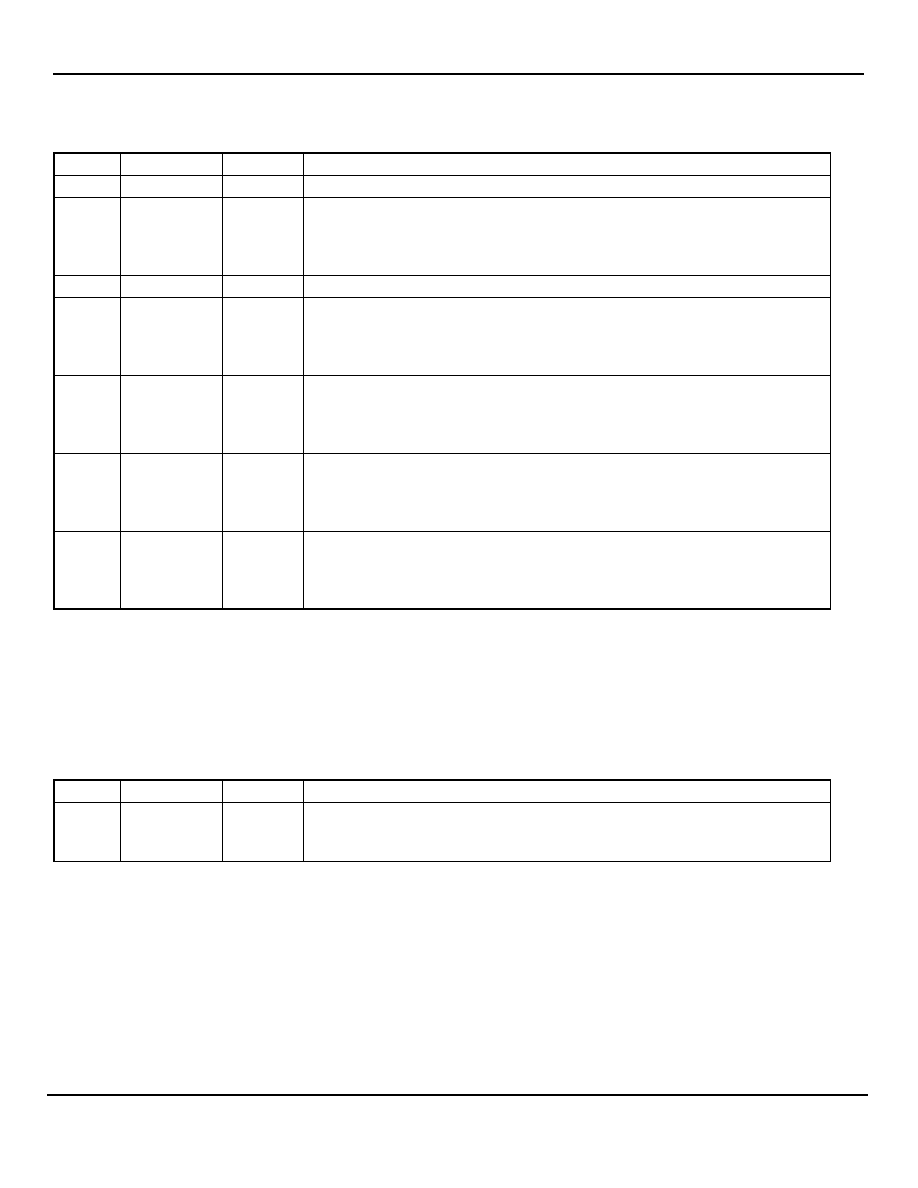

Wakeup Frame Control Register (0x2A – 0x2B): WFCR

This register holds control information programmed by the CPU to control the wake up frame function.

Bit

Default Value

R/W

Description

15-8

0x00

RO

Reserved.

7

0

RW

MPRXE

Magic Packet RX Enable

When set, it enables the magic packet pattern detection.

When reset, the magic packet pattern detection is disabled.

6-4

0x0

RO

Reserved.

3

0

RW

WF3E

Wake up Frame 3 Enable

When set, it enables the Wake up frame 3 pattern detection.

When reset, the Wake up frame 3 pattern detection is disabled.

2

0

RW

WF2E

Wake up Frame 2 Enable

When set, it enables the Wake up frame 2 pattern detection.

When reset, the Wake up frame 2 pattern detection is disabled.

1

0

RW

WF1E

Wake up Frame 1 Enable

When set, it enables the Wake up frame 1 pattern detection.

When reset, the Wake up frame 1 pattern detection is disabled.

0

RW

WF0E

Wake up Frame 0 Enable

When set, it enables the Wake up frame 0 pattern detection.

When reset, the Wake up frame 0 pattern detection is disabled.

0x2C – 0x2F: Reserved

Wakeup Frame 0 CRC0 Register (0x30 – 0x31): WF0CRC0

This register contains the expected CRC values of the Wake up frame 0 pattern.

The value of the CRC calculated is based on the IEEE 802.3 Ethernet standard; it is taken over the bytes specified in

the wake up byte mask registers.

Bit

Default Value

R/W

Description

15-0

0x0000

RW

WF0CRC0

Wake up Frame 0 CRC (lower 16 bits)

The expected CRC value of a Wake up frame 0 pattern.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F24K20-I/SS

IC PIC MCU FLASH 8KX16 28SSOP

PIC16F77-E/ML

IC MCU FLASH 8KX14 A/D 44QFN

PIC16LF74T-I/ML

IC MCU FLASH 4KX14 A/D 44QFN

PIC16F723-I/MV

IC MCU 8BIT 7KB FLASH 28UQFN

PIC18F442T-I/ML

IC MCU FLASH 8KX16 EE A/D 44QFN

PIC18LF2439-I/SP

IC MCU FLASH 6KX16 EE A/D 28DIP

PIC16F687-I/ML

IC PIC MCU FLASH 2KX14 20QFN

PIC18LF2439-I/SO

IC MCU FLASH 6KX16 EE A/D 28SOIC

相关代理商/技术参数

PIC16F77T-I/PT

功能描述:8位微控制器 -MCU 14KB 368 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F77T-I/PTG

功能描述:8位微控制器 -MCU 14KB 368 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F77TIPT

制造商:MICROCHIP 功能描述:New

PIC16F785-E/ML

功能描述:8位微控制器 -MCU 3.5 KB 128 RAM 18I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785-E/P

功能描述:8位微控制器 -MCU 14KB 368 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785-E/SO

功能描述:8位微控制器 -MCU 3.5KB FL 128R 18 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785-E/SS

功能描述:8位微控制器 -MCU 3.5KB FL 128R 18 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785-I/ML

功能描述:8位微控制器 -MCU 3.5 KB 128 RAM 18I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT